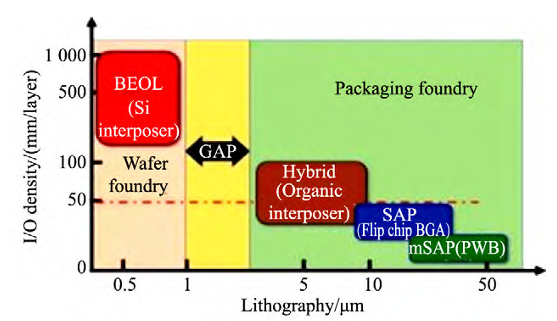

中國粉體網訊 在半導體先進封裝領域,隨著多芯片集成與異構集成需求的不斷攀升,傳統基板材料逐漸難以滿足高密度互連、結構穩定性等核心要求。玻璃基板憑借獨特的材料性能與工藝潛力,正成為突破封裝技術瓶頸的重要解決方案,其在結構設計、制造流程及高密度互連技術上的創新,為高性能芯片封裝提供了新路徑。

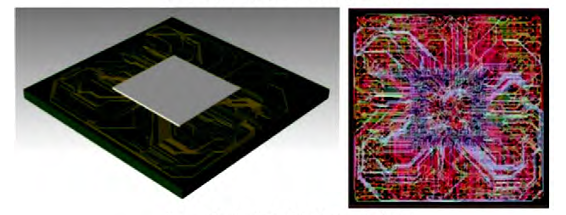

玻璃基板的核心競爭優勢源于其獨特的封裝結構設計。該結構以玻璃為核心層材料,在核心層上下表面構建高密度、細間距金屬布線,布線通過電鍍銅或鎢填充形成,細間距區域則采用薄膜沉積氧化硅作為介質層實現絕緣。這種設計可實現比傳統基板更精細的線寬線距與更高的布線密度,為多芯片間局部高密度互連提供支撐。同時,玻璃基板支持通過倒裝方式實現芯片與基板金屬焊盤的互連,還能在基板內部集成電阻、電容、電感等無源組件,進一步提升封裝集成度。

從材料性能對比來看,玻璃在關鍵參數上顯著優于傳統基板材料,其表面粗糙度低于10nm,熱膨脹系數可在3×10-6~9×10-6K-1之間靈活調節,楊氏模量達50~90GPa,且吸濕性接近于零。這些特性使其在微細布線加工、熱應力控制及結構穩定性方面表現突出,有效解決了傳統有機材料層壓板(如BT、ABF類)在高精度封裝中的短板。

在封裝尺寸上,玻璃基板可實現100mm×100mm的大尺寸加工,為多芯片集成與系統級封裝(SiP)設計提供了更大空間。此外,玻璃面板在面積利用率上的優勢也十分顯著,515mm×510mm、650mm×550mm規格的玻璃面板,有效面積分別是12英寸硅晶圓的3.6倍與4.9倍,大幅提升了單位產能與封裝效率,為芯粒整合創造了有利條件。

在高密度互連技術領域,玻璃基板已形成多類成熟工藝方案,以匹配不同精度需求。當前主流工藝可分為以下三類:

硅基半加成工藝:以TSMC、ASE、Intel為代表,核心是在晶圓表面制備重布線層(RDL)。流程為濺射鈦/銅黏附層與種子層,旋涂PR光刻膠(如JSR111)并曝光露出電鍍區域,最終通過電鍍、濕法去膠、濕法刻蝕完成線路制作。該工藝對種子層黏附性、電鍍均勻性、藥液交換效率要求較高,成本相對較低,適用于線寬/線距≥5μm/5μm的產品。

無機介質層大馬士革工藝:以Amkor為代表,專注于亞微米級金屬布線。先沉積無機介質層并開窗,再整面電鍍金屬,最后通過化學機械拋光(CMP)去除覆銅層。金屬布線嵌入介質層的設計可增強與基材結合力,為實現線寬/線距≤2μm的細間距RDL提供解決方案。

半導體硅基精密工藝:依托半導體硅工藝技術,通過剝離、離子束刻蝕(IBE)、溝槽加工等技術實現精密圖案化。可將線寬與線距均控制在≤2μm,顯著提升互連密度,但對生產條件、設備配置、制造尺寸要求嚴苛,導致成本較高。

玻璃表面布線加工路線及高密度布線樣品 來源:《玻璃基板技術研究進展》(趙瑾等)

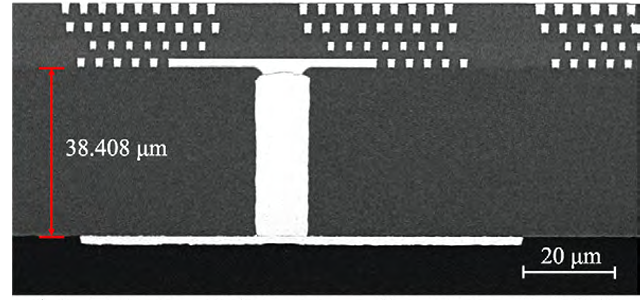

行業實踐已驗證玻璃基板在高密度互連領域的應用潛力。臺積電利用數字光刻與低溫濺射技術,在37cm×47cm玻璃基板上成功堆疊5層RDL,最小線寬達3μm,采用PSPI聚合物作為介質層,側壁傾角約71°,翹曲控制在0.2mm以內;廈門云天半導體則通過大馬士革工藝,在玻璃正面制備出5層無機薄膜介質的RDL互連堆疊結構,最細線寬可達1.5μm。這些成果表明,玻璃基板可通過TGV(玻璃通孔)實現垂直互連,配合高密度RDL滿足高I/O、高帶寬的封裝需求。

最小RDL線寬為1.5μm的5層RDL堆疊結構 來源:云天半導體

隨著人工智能、高性能計算領域對芯片算力的需求持續攀升,先進封裝技術正朝著高集成度、高可靠性的方向加速演進。在此趨勢下,玻璃基板憑借材料性能、工藝靈活性與集成潛力的綜合優勢,有望在未來半導體封裝領域占據更關鍵的地位。

參考來源:

趙瑾.玻璃基板技術研究進展

張興治.玻璃基板在芯片封裝中的應用和性能要求

劉麗敏.基于超薄玻璃襯底的橋連封裝技術研究

(中國粉體網編輯整理/月明)

注:圖片非商業用途,存在侵權告知刪除!